| تحويل العزل الداخلي التفاضلي |  |

| دقة 16 بت | |

| الدقة: دقيقتان زاويتان | |

| ثلاث حالات الإخراج مزلاج | |

| سرعة تتبع عالية مستمرة | |

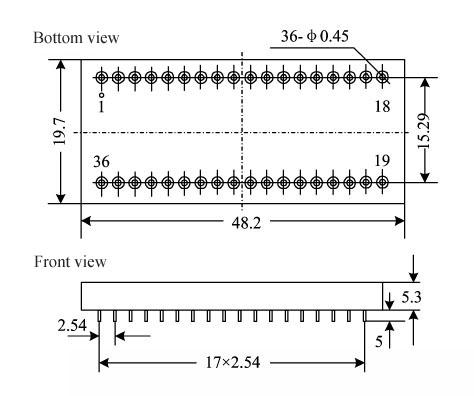

| عبوة DDIP ذات 36 سلكًا ومقاومة للضباب الملحي | |

| Pin-To-Pin متوافق مع طراز SDC14560 لشركة DDC |

| جهاز تحويل متكامل للتتبع المستمر مصمم على | مبدأ مضاعفات النموذج الثاني. تم تصميم منتجات هذه السلسلة و |

| المصنعة بواسطة عملية MCM ، تعتمد العناصر الأساسية شريحة خاصة | |

| تم تطويره بشكل مستقل من قبل معهدنا. ترتيب الدبوس | |

| متوافق مع منتجات سلسلة SDC14560 لشركة DDC الأمريكية ، 16 بت | |

| إخراج مزلاج بيانات الكود الثنائي الطبيعي المتوازي ، 36 سطرًا DIP تمامًا | |

| حزمة معدنية مختومة ، مزايا عالية الدقة ، صغيرة | |

| الحجم ، وانخفاض استهلاك الطاقة ، والوزن الخفيف والموثوقية العالية وما إلى ذلك ، | ويمكن استخدامها على نطاق واسع في أسلحة استراتيجية وتكتيكية مهمة مثل |

| الطائرات ، السفن البحرية ، المدافع ، الصواريخ ، الرادار ، الدبابات ، إلخ. | |

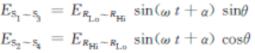

| 4. الأداء الكهربائي (الجدول 1 ، الجدول 2) | |

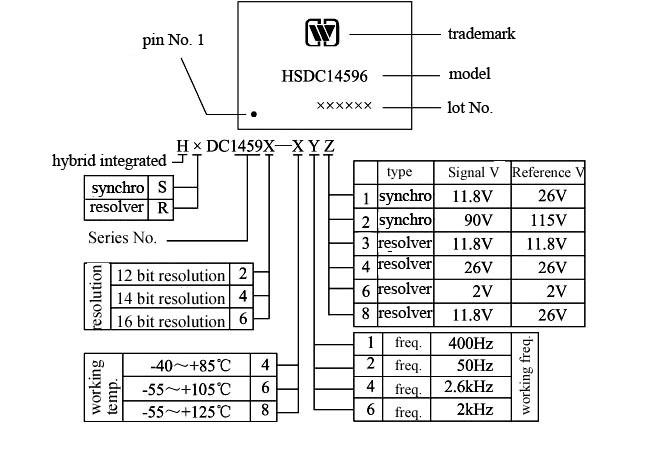

| تزامن مع المحولات الرقمية أو المحلل إلى المحولات الرقمية (سلسلة HSDC / HRDC1459) | |

| الجدول 1 الظروف المصنفة وظروف التشغيل الموصى بها | |

| ماكس المطلق. القيمة المقننة |

| جهد الإشارة V1: القيمة المقدرة ± 20٪ | الجهد المرجعي VRef: القيمة المقدرة ± 20٪ | تردد التشغيل f: القيمة المقدرة ± 20٪ | |

| درجة حرارة التخزين: -65 ~ 150 درجة مئوية | ظروف التشغيل الموصى بها | ||

| جهد الإمداد المنطقي VL: 5 ± 0.5V | جهد الإمداد مقابل: 15 ± 0.75 فولت | ||

| جهد الإشارة V1: القيمة المقدرة ± 10٪ | الجهد المرجعي VRef: القيمة المقدرة ± 20٪ | تردد التشغيل f: القيمة المقدرة ± 20٪ | — |

| نطاق درجة حرارة التشغيل (TA): -55 درجة مئوية ~ 125 درجة مئوية | ملاحظة: * تشير إلى أنه يمكن تخصيصها حسب متطلبات المستخدم. | الجدول 2 الخصائص الكهربائية | معامل |

| الظروف | — | سلسلة HSDC14569 | (VS u003d 15V ، VL u003d + 5V) |

| المعيار العسكري (Q / HW20725-2006) | — | 2V | دقيقة. |

| الأعلى. | — | دقة | نظام ثنائي متوازي كود رقمي |

| 16 بت | — | 2V | صحة |

| ± 10٪ من جهد الإشارة والجهد المرجعي ونطاق تذبذب تردد التشغيل | — | -2 دقيقة زاوية | +2 دقيقة زاوية |

| نطاق التردد المرجعي | — | 50 هرتز | 2600 هرتز |

| نطاق الجهد المرجعي | — | 115 فولت | معاوقة المدخلات المرجعية |

4.4kΩ 4.4kΩ | — | 0 | 129.2 كيلو أوم |

نطاق جهد الإشارة نطاق جهد الإشارة | — | 0 | 90 فولت |

مقاومة مدخلات الإشارة مقاومة مدخلات الإشارة | — | 0 | 4.4kΩ |

| 102.2 كيلو أوم | — | تحول الإشارة / المرحلة المرجعية | -70 درجة |

| + 70 درجة | — | مستوى منطق الإدخال | المنطق "1" ≥3.3V |

| المنطق "0" ≤0.8V | — | إدخال | 0.8 فولت |

| إدخال | — | 0.8 فولت | |

| إدخال | — | — | 0.8 فولت |

| مستوى منطق الإخراج | — | — | المنطق "1" ≥3.3V |

| المنطق "0" ≤0.8V | — | — | إخراج كود الزاوية الرقمية |

| المنطق "1" ≥3.3V | — | — | المنطق "0" ≤0.8V |

| تحويل خرج إشارة الانشغال (CB) | — | 200ns | 600ns |

| إخراج بت كشف الخطأ | المنطق "0" يشير إلى خطأ | — | قدرة التحميل |

| 3TTL | سرعة التتبع | ||

| 2.5rps | ثابت التسارع | ||

| + 10 فولت تيار VS u003d + 15V 10 مللي أمبير |  VS u003d —15 فولت |

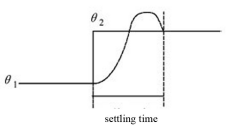

سرعة. تظهر عملية التذبذب للزاوية الرقمية للإخراج في

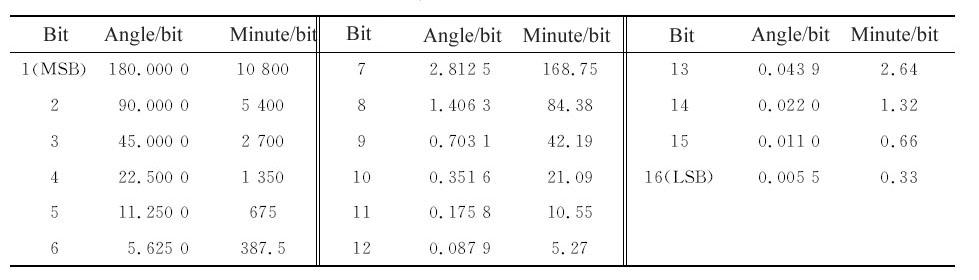

سرعة. تظهر عملية التذبذب للزاوية الرقمية للإخراج في 6. مبدأ التشغيل (الشكل 3)

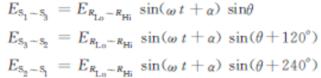

6. مبدأ التشغيل (الشكل 3)| تزامن مع المحولات الرقمية أو المحلل إلى المحولات الرقمية (سلسلة HSDC / HRDC1459) يتم تحويل إشارة إدخال التزامن (أو المحلل) إلى إشارة متعامدة من خلال العزلة التفاضلية الداخلية: | |

Vcos u003d KE0sin (ωt + α) cosθ (كوس)ofحيث ، θ هي زاوية الإدخال التناظرية. الشكل 2 منحنى استجابة الخطوة | هاتان الإشارتان والزاوية الرقمية φ للعداد الداخلي القابل للانعكاسof يتم ضربها في مضاعف دوال الجيب وجيب التمام وهي تم معالجة الخطأ: |

| التضخيم والتمييز الطوري والترشيح التكامل ، إذا | θ-φ ≠ 0 ، سيخرج مذبذب الجهد الذي يتم التحكم فيه النبضات ، و | يعد العداد القابل للانعكاس ، حتى يصبح θ-φ صفرًا ضمن دقة | المحول ، خلال هذه العملية ، يتتبع التحويل تغيير | زاوية الإدخال في كل وقت. | طريقة القراءة: |

| 1 | S1 | الطريقتان التاليتان متاحتان لنقل البيانات: | 25 |  | (1) طريقة المنع: |

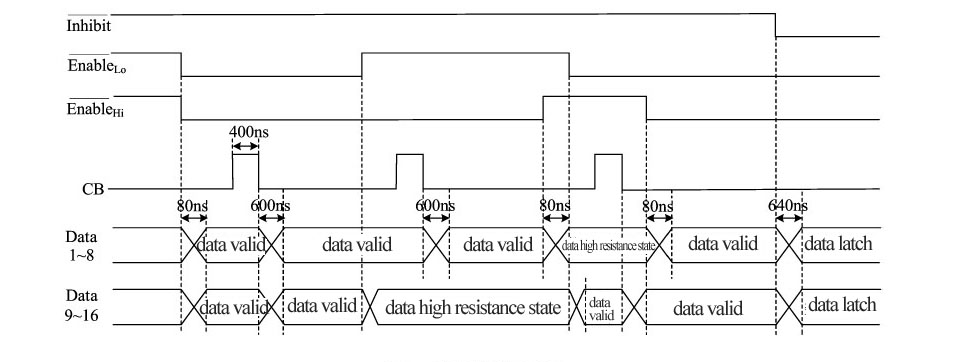

| 2 | S2 | بعد 640ns من | 26 |  | منطق منخفض ، وبيانات الإخراج صالحة ، ويدرك المحول نقل البيانات من خلالها |

| 3 | S3 | و | 27 | . بعد تحرير المنع ، سيقوم النظام تلقائيًا بإنشاء نبضة بعرض يساوي النبضة المشغولة لتحديث البيانات. | (2) وضع التمثال: |

| 4 | S4 | عند الحافة الصاعدة لنبض الانشغال ، يحسب العداد القابل للانعكاس ثلاثي الحالات ؛ عند الحافة الهابطة لنبضة مشغول ، فإنه يولد داخليًا نبضة مزلاج بعرض يساوي نبضة مشغول لتحديث بيانات مزلاج ثلاثي الحالات ، يظهر التسلسل الزمني لنقل البيانات في الشكل 4 ، بمعنى آخر ، بعد 600 نانوثانية. من منطق مشغول منخفض ، يكون النقل المستقر للبيانات صحيحًا. في وضع القراءة غير المتزامن ، يكون الإخراج Busy عبارة عن قطار نبضي على مستوى CMOS. يعتمد عرض مستواه المرتفع والمنخفض على تردد التشغيل وسرعة الدوران للجهاز المحدد. | 28 | VL | الشكل 4 التسلسل الزمني لنقل البيانات |

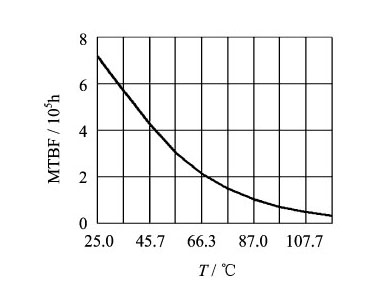

| 7. منحنى MTBF (الشكل 5) | تزامن مع المحولات الرقمية أو المحلل إلى المحولات الرقمية (سلسلة HSDC / HRDC1459) | الشكل 5 منحنى درجة حرارة MTBF | 29 | 8. تعيين دبوس (الشكل 6 ، الجدول 3) | تزامن مع المحولات الرقمية أو المحلل إلى المحولات الرقمية (سلسلة HSDC / HRDC1459) |

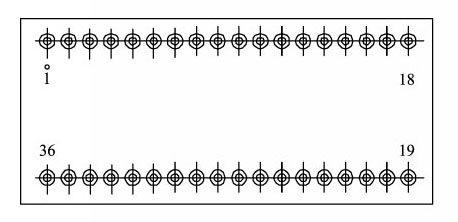

| 19 | الشكل 6 تعيين الدبوس (منظر سفلي) | (ملاحظة: وفقًا لـ GJB / Z299B-98 ، حالة الأرض الجيدة المتوخاة) | 30 | NC | الجدول 3 تعيين دبوس |

| 20 | RL | دبوس | 31 | رمز | المعنى |

| 21 | دبوس | رمز | 32 | VS | المعنى |

| 22 | إدخال محلل S1 (أو إدخال متزامن S1) | تمكين رقمي للتحكم في أقل من 8 بت | 33 | إدخال محلل S2 (أو إدخال متزامن S2) | تحكم رقمي ممكّن لـ 8 بت أعلى |

| 23 | إدخال محلل S3 (أو إدخال متزامن S3) | ريبلك | 34 | خرج إشارة صفرية بت | إدخال محلل S4 (اتركه غير متصل) |

| 24 | CB | + 5V امدادات الطاقة | 5 18 | NC | D1-D14 |

| الإخراج الرقمي 1 (MSB) -14 | GND |

| أرض | RHi |

| نهاية عالية لإدخال إشارة مرجعية | لا يوجد اتصال |

| RL | نهاية منخفضة لإدخال إشارة مرجعية |

-ضد

-ضد -15V امدادات الطاقة

-15V امدادات الطاقة

D15 الإخراج الرقمي 15

الإخراج الرقمي 15 ).

).

+ 15V امدادات الطاقة

D16

الخرج الرقمي 16 (LSB)

تعيق

إدخال إشارة ثابتة

فيل

S1 ، S2 ، S3 ، S4

S1 ، S2 ، S3 ، S4

نهاية منخفضة لإدخال إشارة مرجعيةofأدنى | إدخال إشارة تمكين رقم 8 بت ، هذا الدبوس هو دبوس الإدخال المنطقي لـofالتحكم في بوابات البيانات ، وتتمثل مهمتها في تنفيذ سيطرة ثلاث حالات |

|  |

| خارجيا على بيانات الإخراج أقل من 8 بت للمحول. المستوى المنخفض هو | صحيح ، فإن بيانات الإخراج ذات 8 بت الأقل للمحول تشغل البيانات |

حالة المقاومة ، والجهاز لا يشغل ناقل البيانات. ممكنووقت تأخير الإصدار هو 600 نانو ثانية (كحد أقصى). | أعلى | إدخال إشارة تمكين رقم 8 بت ، هذا الدبوس هو دبوس الإدخال المنطقي لـ | التحكم في بوابات البيانات ، وتتمثل مهمتها في تنفيذ سيطرة ثلاث حالات | خارجيًا على بيانات الإخراج الأعلى 8 بت للمحول. مستوى منخفض | صالح ، فإن بيانات الإخراج الأعلى 8 بت للمحول تحتلمركبة البيانات؛ في المستوى العالي ، يكون دبوس بيانات الإخراج الأعلى 8 بت مرتفعًا | حالة المقاومة ، والجهاز لا يشغل ناقل البيانات. ممكن | ووقت تأخير الإصدار هو 600 نانو ثانية (كحد أقصى). | منع الكهرباء الساكنة |

إدخال الإشارة ، هذا الدبوس هو دبوس الإدخال لمنطق التحكم ، وظيفته | هو إخراج البيانات خارجيًا إلى المحول لتحقيق اختياري | Niالإغلاق أو التحكم في التجاوز. على مستوى عالٍ ، تكون بيانات الإخراج الخاصة بـ | المحول المخرجات مباشرة دون الإغلاق ؛ عند مستوى منخفض ، الناتج | تم إغلاق بيانات المحول ، ولا يتم تحديث البيانات ، ولكن ملفلا تتم مقاطعة الحلقة الداخلية ، ويعمل التعقب في جميع ملفات | الوقت ، قام Inhibit بتوصيل مقاومة السحب داخليًا. بعد تأخير 600ns (كحد أقصى) لـ | Au الحافة الهابطة للإشارة الثابتة ، تصبح البيانات مستقرة (سواء كان | يشغل الجهاز ناقل البيانات ، أي عندما يتوقف إخراج البياناتفي ولاية | وخرج إشارة CB "Busy" ، تشير هذه الإشارة إلى ما إذا كانت الشفرة الثنائية |

X

X